I am planning to get rid of Windows 10 due to all the slowness artificially created by billgates to extract more money from users.

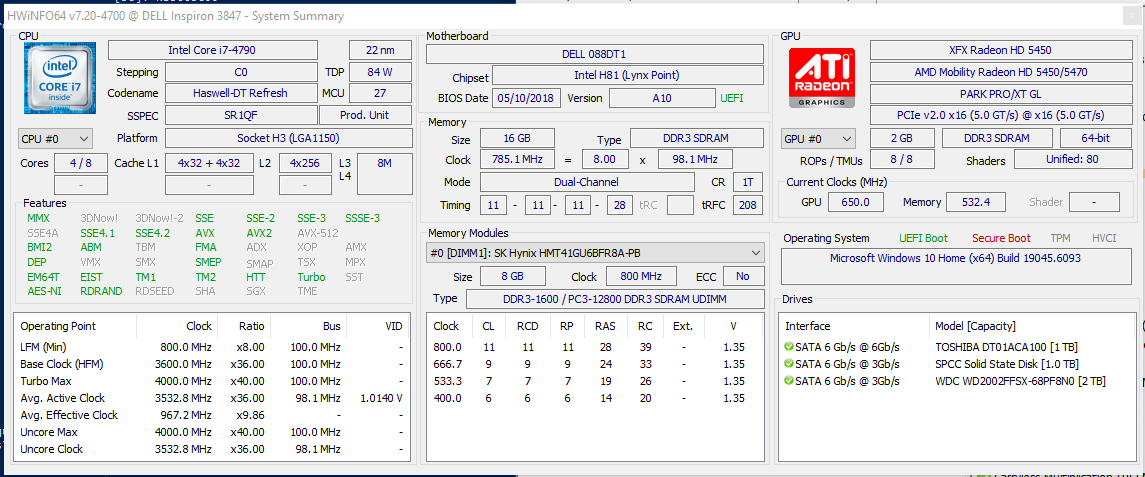

I am planning for “Qube OS” but it has requirement that, the CPU and board should support: VT-x and VT-d. When I run HWInfo app It shows VMX (VM-x ?) as disabled. and VT-d as enabled. Intel website also tells that for this CPU the feature is vendor dependent. So Can someone tell from below data whether this PC (mobo + CPU) support VT-x and VT-d for sure?

Thank you.

Dell Inspiron 3847

CPU details:

General Information

Processor Name: Intel Core i7-4790

Original Processor Frequency: 3600.0 MHz

CPU ID: 000306C3

CPU Brand Name: Intel(R) Core(TM) i7-4790 CPU @ 3.60GHz

CPU Vendor: GenuineIntel

CPU Stepping: C0

CPU Code Name: Haswell-DT Refresh

CPU Technology: 22 nm

CPU S-Spec: SR1QF

CPU Thermal Design Power (TDP): 84.0 W

CPU Thermal Design Current (TDC): 95.0 A

CPU Power Limits (Max): Power = Unlimited, Time = Unlimited

CPU Power Limit 1 (Long Duration)/Processor Base Power (PBP): Power = 84.00 W, Time = 8.00 sec [Locked]

CPU Power Limit 2 (Short Duration)/Maximum Turbo Power (MTP): Power = 105.00 W, Time = 2.44 ms [Locked]

CPU Max. Junction Temperature (Tj,max): 100 °C

CPU Type: Production Unit

CPU Platform: Socket H3 (LGA1150)

Microcode Update Revision: 27

Number of CPU Cores: 4

Number of Logical CPUs: 8

Operating Points

CPU LFM (Minimum): 800.0 MHz = 8 x 100.0 MHz

CPU HFM (Base): 3600.0 MHz = 36 x 100.0 MHz

CPU Turbo Max: 4000.0 MHz = 40 x 100.0 MHz [Unlocked]

Turbo Ratio Limits: 40x (1-2c), 39x (3c), 38x (4c)

CPU Current: 3532.8 MHz = 36 x 98.1 MHz @ 1.0123 V

LLC/Ring Maximum: 4000.0 MHz = 40.00 x 100.0 MHz

LLC/Ring Current: 3827.2 MHz = 39.00 x 98.1 MHz

CPU Bus Type: Intel Direct Media Interface (DMI) v2.0

Maximum DMI Link Speed: 5.0 GT/s

Current DMI Link Speed: 5.0 GT/s

IA Overclocking

Voltage Offset: Supported

Voltage Override: Supported

Ratio Overclocking: Not Supported

Fused Ratio Limit: 40x

OC Ratio Limit: N/A

Voltage Mode: Adaptive

Voltage Offset: 0 mV

GT Overclocking

Voltage Offset: Supported

Voltage Override: Supported

Ratio Overclocking: Supported

Fused Ratio Limit: 57x

OC Ratio Limit: N/A

Voltage Mode: Adaptive

Voltage Offset: 0 mV

CLR (CBo/LLC/Ring) Overclocking

Voltage Offset: Supported

Voltage Override: Supported

Ratio Overclocking: Not Supported

Fused Ratio Limit: 40x

OC Ratio Limit: N/A

Voltage Mode: Adaptive

Voltage Offset: 0 mV

Uncore/SA Overclocking

Voltage Offset: Supported

Voltage Override: Not Supported

Ratio Overclocking: Not Supported

Fused Ratio Limit: N/A

OC Ratio Limit: N/A

Voltage Mode: Adaptive

Voltage Offset: 0 mV

Analog IO Overclocking

Voltage Offset: Supported

Voltage Override: Not Supported

Ratio Overclocking: Not Supported

Fused Ratio Limit: N/A

OC Ratio Limit: N/A

Voltage Mode: Adaptive

Voltage Offset: 0 mV

Digital IO Overclocking

Voltage Offset: Supported

Voltage Override: Not Supported

Ratio Overclocking: Not Supported

Fused Ratio Limit: N/A

OC Ratio Limit: N/A

Voltage Mode: Adaptive

Voltage Offset: 0 mV

Cache and TLB

L1 Cache: Instruction: 4 x 32 KBytes, Data: 4 x 32 KBytes

L2 Cache: Integrated: 4 x 256 KBytes

L3 Cache: 8 MBytes

Instruction TLB: 2MB/4MB Pages, Fully associative, 8 entries

Data TLB: 4 KB Pages, 4-way set associative, 64 entries

Standard Feature Flags

FPU on Chip Present

Enhanced Virtual-86 Mode Present

I/O Breakpoints Present

Page Size Extensions Present

Time Stamp Counter Present

Pentium-style Model Specific Registers Present

Physical Address Extension Present

Machine Check Exception Present

CMPXCHG8B Instruction Present

APIC On Chip / PGE (AMD) Present

Fast System Call Present

Memory Type Range Registers Present

Page Global Feature Present

Machine Check Architecture Present

CMOV Instruction Present

Page Attribute Table Present

36-bit Page Size Extensions Present

Processor Number Not Present

CLFLUSH Instruction Present

Debug Trace and EMON Store Not Present

Internal ACPI Support Present

MMX Technology Present

Fast FP Save/Restore (IA MMX-2) Present

Streaming SIMD Extensions Present

Streaming SIMD Extensions 2 Present

Self-Snoop Present

Multi-Threading Capable Present

Automatic Clock Control Present

IA-64 Processor Not Present

Signal Break on FERR Present

Virtual Machine Extensions (VMX) Not Present

Safer Mode Extensions (Intel TXT) Not Present

Streaming SIMD Extensions 3 Present

Supplemental Streaming SIMD Extensions 3 Present

Streaming SIMD Extensions 4.1 Present

Streaming SIMD Extensions 4.2 Present

AVX Support Present

Fused Multiply Add (FMA) Present

Carryless Multiplication (PCLMULQDQ)/GFMUL Present

CMPXCHG16B Support Present

MOVBE Instruction Present

POPCNT Instruction Present

XSAVE/XRSTOR/XSETBV/XGETBV Instructions Present

XGETBV/XSETBV OS Enabled Present

Float16 Instructions Present

AES Cryptography Support Present

Random Number Read Instruction (RDRAND) Present

Extended xAPIC Not Present

MONITOR/MWAIT Support Not Present

Thermal Monitor 2 Present

Enhanced SpeedStep Technology Present

L1 Context ID Not Present

Send Task Priority Messages Disabling Present

Processor Context ID Present

Direct Cache Access Not Present

TSC-deadline Timer Not Present

Performance/Debug Capability MSR Present

IA32 Debug Interface Support Not Present

64-Bit Debug Store Not Present

CPL Qualified Debug Store Not Present

Extended Feature Flags

64-bit Extensions Present

RDTSCP and TSC_AUX Support Present

1 GB large page support Present

No Execute Present

SYSCALL/SYSRET Support Present

Bit Manipulation Instructions Set 1 Present

Bit Manipulation Instructions Set 2 Present

Advanced Vector Extensions 2 (AVX2) Present

Advanced Vector Extensions 512 (AVX-512) Foundation Not Present

AVX-512 Prefetch Instructions Not Present

AVX-512 Exponential and Reciprocal Instructions Not Present

AVX-512 Conflict Detection Instructions Not Present

AVX-512 Doubleword and Quadword Instructions Not Present

AVX-512 Byte and Word Instructions Not Present

AVX-512 Vector Length Extensions Not Present

AVX-512 52-bit Integer FMA Instructions Not Present

Secure Hash Algorithm (SHA) Extensions Not Present

Software Guard Extensions (SGX) Support Not Present

Supervisor Mode Execution Protection (SMEP) Present

Supervisor Mode Access Prevention (SMAP) Not Present

Hardware Lock Elision (HLE) Not Present

Restricted Transactional Memory (RTM) Not Present

Memory Protection Extensions (MPX) Not Present

Read/Write FS/GS Base Instructions Present

Enhanced Performance String Instruction Present

INVPCID Instruction Present

RDSEED Instruction Not Present

Multi-precision Add Carry Instructions (ADX) Not Present

PCOMMIT Instructions Not Present

CLFLUSHOPT Instructions Not Present

CLWB Instructions Not Present

TSC_THREAD_OFFSET Present

Platform Quality of Service Monitoring (PQM) Not Present

Platform Quality of Service Enforcement (PQE) Not Present

FPU Data Pointer updated only on x87 Exceptions Not Present

Deprecated FPU CS and FPU DS Present

Intel Processor Trace Not Present

PREFETCHWT1 Instruction Not Present

AVX-512 Vector Bit Manipulation Instructions Not Present

AVX-512 Vector Bit Manipulation Instructions 2 Not Present

AVX-512 Galois Fields New Instructions Not Present

AVX-512 Vector AES Not Present

AVX-512 Vector Neural Network Instructions Not Present

AVX-512 Bit Algorithms Not Present

AVX-512 Carry-Less Multiplication Quadword (VPCLMULQDQ) Not Present

AVX-512 Vector POPCNT (VPOPCNTD/VPOPCNTQ) Not Present

User-Mode Instruction Prevention Not Present

Protection Keys for User-mode Pages Not Present

OS Enabled Protection Keys Not Present

Wait and Pause Enhancements (WAITPKG) Not Present

Total Memory Encryption Not Present

Key Locker Not Present

57-bit Linear Addresses, 5-level Paging Not Present

Read Processor ID Not Present

Cache Line Demote Not Present

MOVDIRI: Direct Stores Not Present

MOVDIR64B: Direct Stores Not Present

ENQCMD: Enqueue Stores Not Present

SGX Launch Configuration Not Present

Protection Keys for Supervisor-Mode Pages Not Present

Control-Flow Enforcement Technology (CET) Shadow Stack Not Present

AVX-512 4 x Vector Neural Network Instructions Word Variable Precision Not Present

AVX-512 4 x Fused Multiply Accumulation Packed Single Precision Not Present

Fast Short REP MOV Not Present

User Interrupts Not Present

AVX-512 VP2INTERSECT Support Not Present

AVX-512 FP16 Not Present

MD_CLEAR Support Present

Restricted Transactional Memory (RTM) Always Abort Not Present

SERIALIZE Not Present

Hybrid Processor Not Present

TSX Suspend Load Address Tracking Not Present

Platform Configuration (PCONFIG) Not Present

Indirect Branch Restricted Speculation (IBRS), Indirect Branch Predictor Barrier (IBPB)Present

Single Thread Indirect Branch Predictors (STIBP) Present

L1D_FLUSH Support Present

IA32_ARCH_CAPABILITIES MSR Present

IA32_CORE_CAPABILITIES MSR Not Present

Speculative Store Bypass Disable (SSBD) Present

Control-Flow Enforcement Technology (CET) Indirect Branch Tracking Not Present

Advanced Matrix Extensions (AMX) Tile Architecture Not Present

Advanced Matrix Extensions (AMX) bfloat16 Support Not Present

Advanced Matrix Extensions (AMX) 8-bit Integer Operations Not Present

AVX (VEX-encoded) Vector Neural Network Instructions Not Present

AVX-512 BFLOAT16 Instructions Not Present

Fast Zero-Length MOVSB Not Present

Fast Short STOSB Not Present

Fast Short CMPSB, SCASB Not Present

History Reset Not Present

Linear Address Masking Not Present

Protected Processor Inventory Number (IA32_PPIN) Support Not Present

Vulnerability Mitigation Mechanisms

Rogue Data Cache Load (RDCL) Susceptible

Speculative Store Bypass (SSB) Susceptible

Microarchitectural Data Sampling (MDS) Susceptible

MCE on modifying code page size without TLB invalidation Susceptible

Transactional Asynchronous Abort (TAA) Affected

Indirect Branch Restriction Speculation (IBRS) Not Supported

RSB Alternate Not Supported

L1D Flush on VM Entry Not Needed Not Supported

Energy Filtering Control Not Supported

Enhanced Features

Thermal Monitor 1: Supported, Enabled

Thermal Monitor 2: Supported, Enabled

Enhanced Intel SpeedStep (GV3): Supported, Enabled

Bi-directional PROCHOT#: Enabled

Extended Auto-HALT State C1E: Enabled

MLC Streamer Prefetcher Supported, Enabled

MLC Spatial Prefetcher Supported, Enabled

DCU Streamer Prefetcher Supported, Enabled

DCU IP Prefetcher Supported, Enabled

Intel Dynamic Acceleration (IDA) Technology: Not Supported

Intel Dynamic FSB Switching: Not Supported

Intel Turbo Boost Technology: Supported, Enabled

Programmable Ratio Limits: Supported, Disabled

Programmable TDC/TDP Limits: Supported, Disabled

Hardware Duty Cycling: Not Supported

Intel Speed Select: Not Supported

CPU SKU Features

Internal Graphics: Supported

ECC: Not Supported

VT-d: Supported

2 DIMMs per Channel: Not Supported

X2APIC: Supported

Dual Channel: Supported

BCLK Coarse Ratio Support (PCIe Ratio Changing): Not Supported

DDR Overclocking: Not Supported

Overclocking: Not Supported

Overclocking: Disabled

DMI Width: x4

DMI Gen 2 Mode: Supported

Camarillo Device: Not Supported

Display HD Audio: Supported

DDR3L: Supported

Maximum Memory Size per Channel: 16 GB

DDR3 Frequency Support (100 MHz RefClk): 800 MHz (DDR3-1600)

Additive Graphics: Supported

Additive Graphics: Enabled

PCIe Gen 3: Not Supported

PCIe x16 Port: Supported

SOFTBIN: Not Supported

Voltage Regulator (SVID)

VCC VR: ON Semi NCP81119, VR12.5

VR Thermal Sensor: Supported

Memory Ranges

Maximum Physical Address Size: 39-bit (512 GBytes)

Maximum Virtual Address Size: 48-bit (256 TBytes)

MTRRs

Range 0-400000000 (0MB-16384MB) Type: Write Back (WB)

Range 400000000-410000000 (16384MB-16640MB) Type: Write Back (WB)

Range 410000000-418000000 (16640MB-16768MB) Type: Write Back (WB)

Range 418000000-41C000000 (16768MB-16832MB) Type: Write Back (WB)

Range 41C000000-41E000000 (16832MB-16864MB) Type: Write Back (WB)

Range 41E000000-41F000000 (16864MB-16880MB) Type: Write Back (WB)

Range E0000000-100000000 (3584MB-4096MB) Type: Uncacheable (UC)